TSMC Urging Customers to Apply for N2 Node Allocation as It's Almost Full Until 2027

•March 2, 2026

0

Why It Matters

The bottleneck on TSMC’s advanced N2 node threatens to delay product launches and inflate semiconductor costs across the industry.

Key Takeaways

- •N2 node booked through 2027, limited remaining capacity

- •Six‑quarter lead time for new allocations, 12‑month delivery

- •NVIDIA biggest TSMC customer, still faces constraints

- •Hot‑lot runs cost premium, no guaranteed timing

- •Delays may push products out of market viability

Pulse Analysis

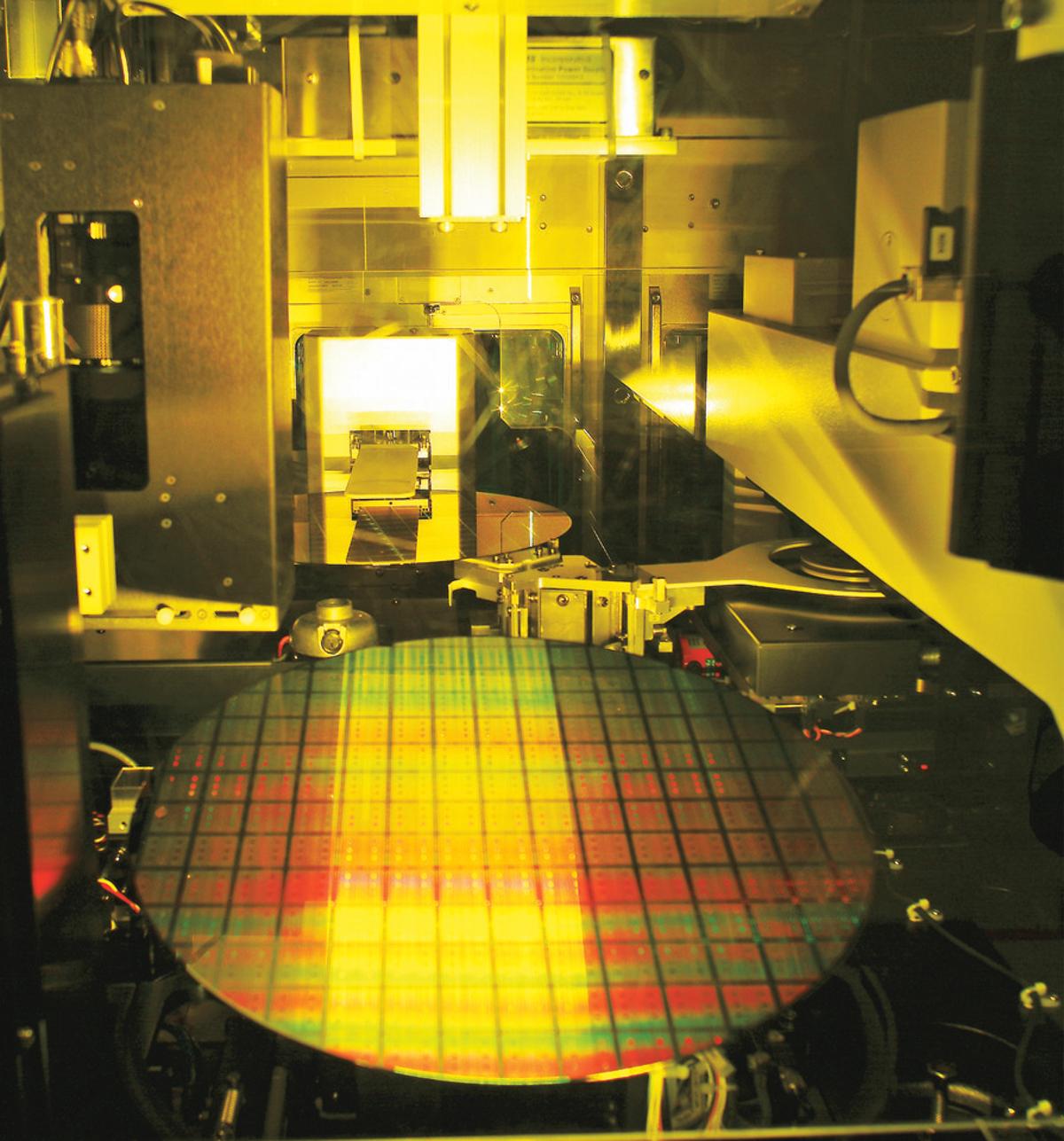

TSMC’s N2 node represents the cutting edge of 5‑nanometer class manufacturing, a critical platform for high‑performance computing, AI accelerators, and next‑generation mobile chips. By the end of 2027, the foundry’s capacity is essentially saturated, leaving only a narrow window for new orders. This scarcity reflects the surging demand from data‑center giants and the broader semiconductor renaissance, but it also forces customers to plan years in advance, reshaping the traditional product‑development cadence.

For customers, the elongated lead times translate into strategic headaches. NVIDIA, now TSMC’s top client, must navigate a twelve‑month gap between wafer start and final delivery, potentially throttling its roadmap for GPUs and AI processors. Smaller fabless firms face even steeper challenges, as the six‑quarter waiting period can render product launches financially untenable. While TSMC offers "hot‑lot" or "hot‑run" options at a premium, these ad‑hoc runs lack timing guarantees, making them a risky stop‑gap for time‑sensitive projects.

The broader market feels the ripple effects of this capacity crunch. Companies may reconsider design migrations to alternative nodes, explore rival foundries, or accelerate investment in in‑house silicon to mitigate dependence on TSMC’s N2 pipeline. Investors watch these dynamics closely, as prolonged shortages could compress margins, delay revenue recognition, and shift competitive advantage toward firms with secured access. In this environment, proactive allocation requests and flexible supply‑chain strategies become essential for maintaining product relevance and financial performance.

TSMC Urging Customers to Apply for N2 Node Allocation as it's Almost Full Until 2027

0

Comments

Want to join the conversation?

Loading comments...