Silicon-On-Insulator Achieves Coupled Colour Centre Formation for Photon Sources

Key Takeaways

- •Annealing 525 °C optimally activates T‑centres in SOI

- •Carbon/hydrogen implantation yields high‑density W and G centres

- •Plasma cleaning reduces T‑centre density, mitigated by remote ashing

- •CN colour centre identified, promising for quantum networking

- •Process parameters differ from prior reports, enabling stable emitters

Pulse Analysis

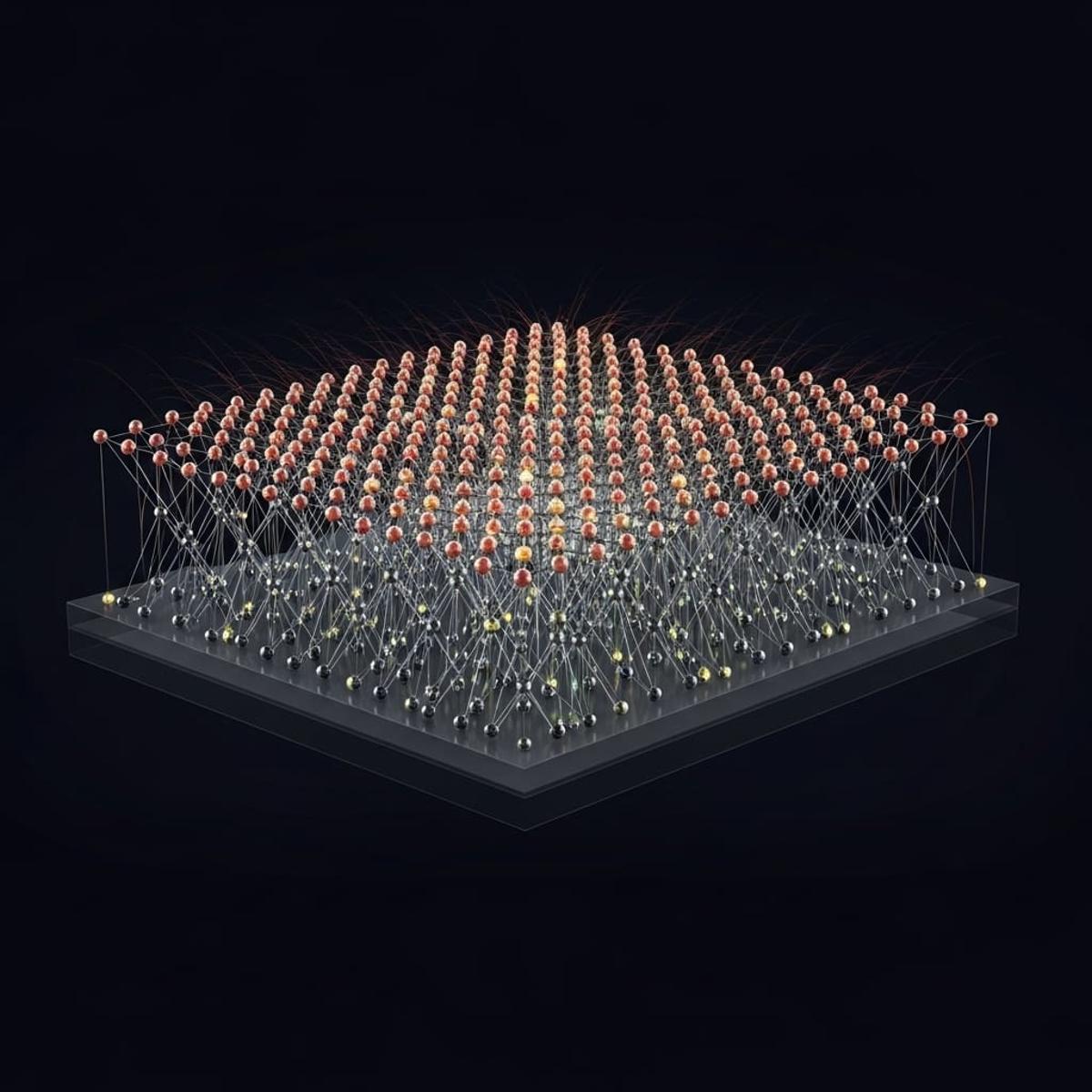

Colour centres in silicon have emerged as a promising route to integrate quantum light sources directly onto semiconductor chips. Their atom‑like emission lines, long spin coherence, and compatibility with mature CMOS processes make them attractive for quantum communication and computing. However, achieving reproducible defect formation in silicon‑on‑insulator (SOI) has been hampered by the sensitivity of these centres to implantation damage, annealing schedules, and nanofabrication steps. A reliable fabrication recipe is therefore a critical bottleneck for commercial quantum photonics.

The Copenhagen team tackled this bottleneck by combining carbon and hydrogen ion implantation with a systematic annealing matrix ranging from 200 °C to 600 °C and dwell times of 30 to 600 seconds. Their data pinpointed 525 °C as the sweet spot for activating T‑centres, while a 7 × 10¹³ cm⁻² carbon fluence and a brief 1000 °C curing anneal maximized the density of W and G emitters. Crucially, they observed inter‑dependent dynamics—certain centres could be suppressed or revived by adjusting temperature— and identified the CN centre, a SiCC defect with a sharp zero‑phonon line suitable for quantum networking.

These process insights translate directly into a manufacturing advantage for silicon‑based quantum devices. By avoiding aggressive plasma cleaning and favoring remote ashing, fab lines can preserve T‑centre populations, while the newly characterized CN centre expands the toolbox for spin‑photon interfaces. The ability to reliably produce multiple, spectrally distinct emitters on a 220 nm SOI wafer paves the way for dense photonic integrated circuits, on‑chip single‑photon sources, and multi‑spin registers. Industry players can now accelerate product roadmaps for secure communication, quantum sensors, and scalable quantum processors.

Silicon-On-Insulator Achieves Coupled Colour Centre Formation for Photon Sources

Comments

Want to join the conversation?