Recent Posts

Video•Feb 28, 2026

Digital Design & Comp. Arch: L4: Sequential Logic Design & Finite State Machines (Spring 2026)

The lecture continued the Digital Design course by completing the discussion of sequential logic and introducing finite state machines (FSMs). After reviewing memory elements—from cross‑coupled inverters to gated D‑latches and multi‑bit memory arrays—the professor emphasized the need for storage elements that can remember past inputs, setting the stage for state‑based design. Key insights included the distinction between combinational and sequential systems, illustrated with a combination‑lock example that required a specific input sequence to transition through states A, B, C, and D before unlocking. The instructor highlighted how FSMs capture these transitions, and explained that the lock operates as an asynchronous machine, reacting immediately to inputs, whereas modern computers favor synchronous designs that rely on a clock to coordinate state changes and ensure reliable timing. Notable details featured a practical discussion of extra‑credit policy (a 1% grade boost), the hardware cost growth from a four‑transistor inverter to a 20‑transistor gated latch, and the upcoming lab focus on Verilog, timing analysis, and FPGA prototyping. Student questions clarified the lock’s behavior and the difference between asynchronous and synchronous state transitions. The implications are clear: mastering FSM design and timing concepts is essential for building reliable digital systems, and the forthcoming labs will provide hands‑on experience with hardware description languages and real silicon implementation, preparing students for industry‑level digital design challenges.

By Onur Mutlu Lectures

Video•Feb 26, 2026

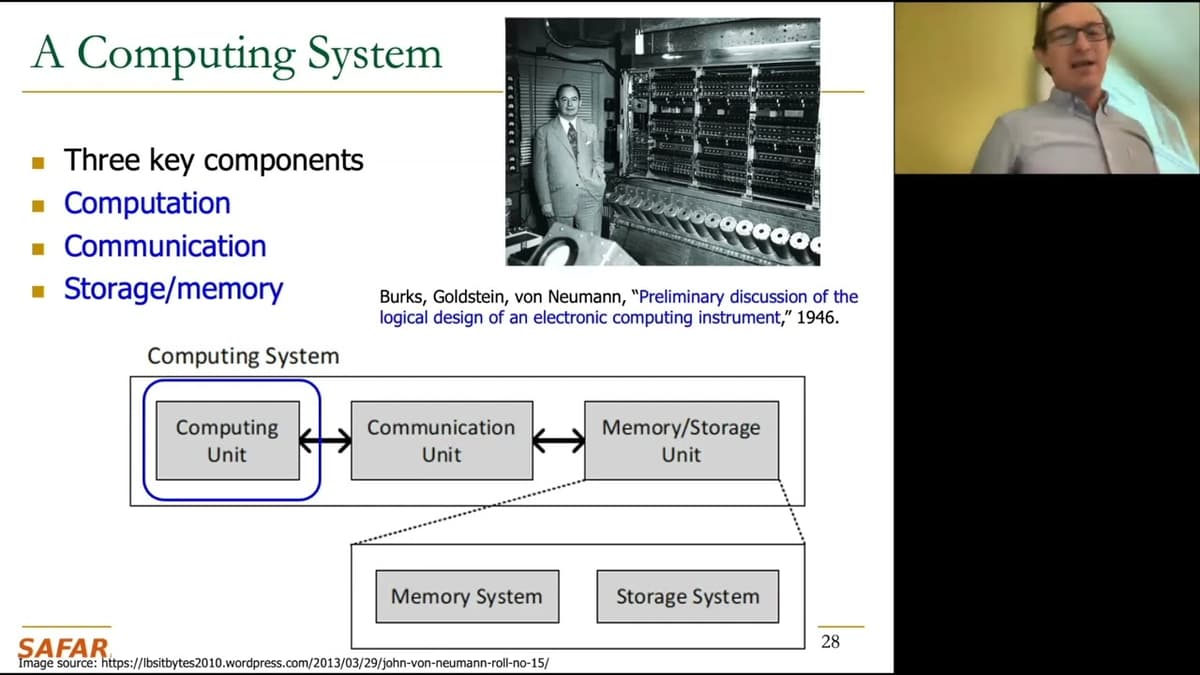

P&S Understanding and Designing Modern Storage Systems - L1: Course Introduction (Spring 2026)

The video introduces the Spring 2026 iteration of the "Understanding and Designing Modern Storage Systems" course, led by Professor Onur Mutlu’s Safari Research Group at ETH Zurich, along with instructors Rakesh Nadig and Dr. Mohamed Sadati. It outlines the team’s...

By Onur Mutlu Lectures

Video•Feb 25, 2026

P&S: Architectures & Algorithms for Health & Life Sciences - L1: Course Introduction (Spr 2026)

Welcome to the first lecture of the ETH Zurich “Architectures & Algorithms for Health and Life Sciences” project‑seminar, presented by PhD candidate Nika Mansuriyasi. The session outlines the course’s scope, objectives, and its relevance amid accelerating biotechnological data generation. Mansuriyasi explains...

By Onur Mutlu Lectures

Video•Feb 25, 2026

Digital Design & Computer Architecture - Problem Solving III (Spring 2022)

On July 19, 2022 Professor Onur Mutlu delivered the third problem‑solving lecture for ETH Zürich’s Digital Design & Computer Architecture spring 2022 course. The session’s slide deck and video are available online, alongside a curated list of seminal papers on...

By Onur Mutlu Lectures

Video•Feb 24, 2026

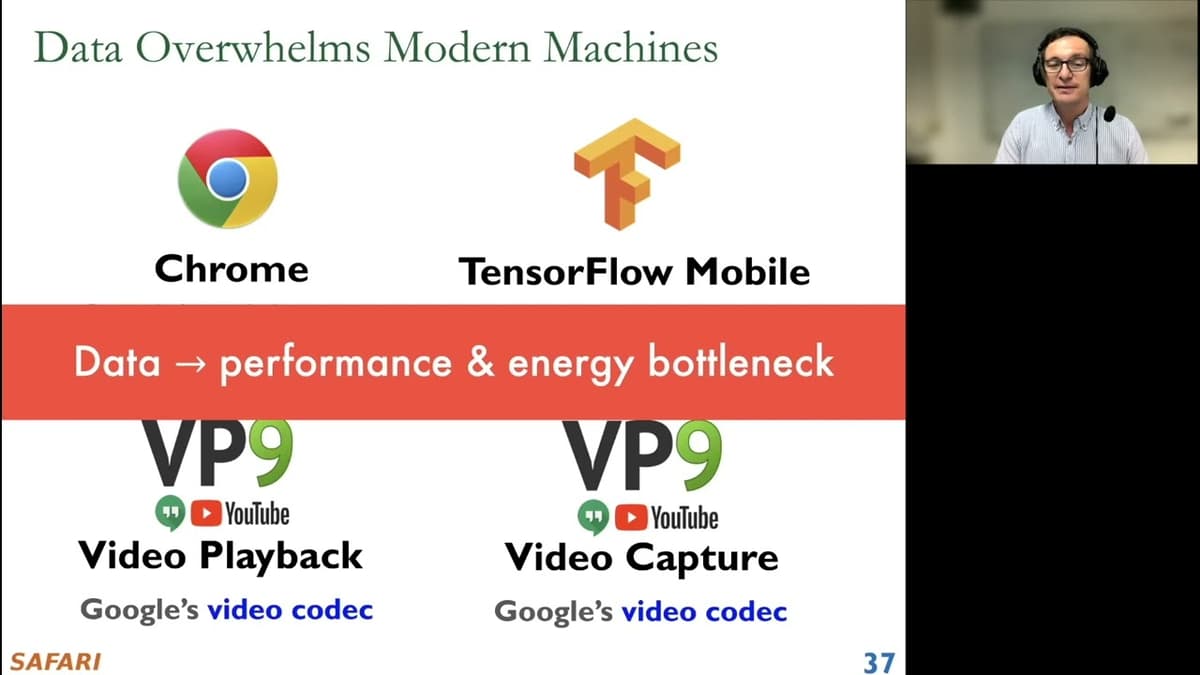

Memory-Centric Computing - Talk at IEEE Custom Integrated Circuits Conference - Prof. Onur Mutlu

Prof. Onur Mutlu opened the IEEE Custom Integrated Circuits talk by framing memory‑centric computing as a response to exploding data volumes in AI, genomics, and other data‑intensive workloads. He highlighted that while CPUs, GPUs, and accelerators have grown more powerful,...

By Onur Mutlu Lectures

Video•Feb 24, 2026

Digital Design & Computer Architecture - Problem Solving II (Spring 2022)

The video walks through a textbook‑style problem on branch prediction and then shifts to designing a systolic array for matrix multiplication, illustrating two core concepts in computer architecture. It defines locally correlated branches—where knowledge of a previous iteration predicts the current...

By Onur Mutlu Lectures

Video•Feb 23, 2026

Memory-Centric Computing - Winter School on Operating Systems (WSOS) Opening Talk - 03.04.2023

In his opening talk at the Winter School on Operating Systems, Prof. Onur Mutlu introduced Memory‑Centric Computing, a paradigm that repositions memory from a passive storage element to an active compute resource. He highlighted the performance and energy penalties of...

By Onur Mutlu Lectures

Video•Feb 23, 2026

Digital Design & Computer Architecture - Problem Solving I (Spring 2022)

ETH Zürich’s Digital Design and Computer Architecture course released a new Problem Solving I session on July 5, 2022, led by Professor Onur Mutlu. The 2‑hour lecture walks through key topics such as finite‑state machines, the MIPS ISA, dataflow, pipelining,...

By Onur Mutlu Lectures

Video•Feb 20, 2026

Digital Design & Computer Architecture - Lecture 27: Epilogue (Spring 2022)

The video serves as the concluding epilogue of a Spring 2022 digital design and computer architecture course, reviewing the material covered and emphasizing the central role of critical thinking in hardware design. It recaps the curriculum—from transistors to virtual memory, instruction...

By Onur Mutlu Lectures

Video•Feb 19, 2026

Digital Design & Computer Architecture - Lecture 26a: Virtual Memory II (Spring 2022)

The lecture expands on virtual memory implementation details, focusing on page-table size and storage using multi-level page tables, x86-64’s 64-bit page-table entries, and support for multiple page sizes (4KB, 2MB, 1GB). It reviews control registers (e.g., CR3), context-switch implications for...

By Onur Mutlu Lectures

Video•Feb 19, 2026

Digital Design & Comp. Arch. - Lecture 26: Virtual Memory (Spring 2022)

Professor introduces virtual memory as a core OS–architecture interface, tracing its roots to 1960s ideas and contrasting its relatively little evolution with the rapid advances in prefetching. The lecture previews key VM concepts, implementation complexity, and performance overheads, and highlights...

By Onur Mutlu Lectures

Video•Feb 18, 2026

Digital Design & Comp. Arch: L2: Transistors, Gates, Combinational Logic (Spring 2026)

The lecture introduced the fundamentals of digital design by tracing the evolution from individual MOS transistors to combinational logic circuits. It emphasized that modern computers are built from billions of transistors, citing the Intel 4004’s 2,300 transistors, the Pentium 4’s 42 million,...

By Onur Mutlu Lectures

Video•Feb 18, 2026

Memory-Centric Computing - Invited Talk - Systems Research Community @ France - 29.11.2022

In an invited talk on memory-centric computing, ETH professor Uno (likely Onur?) argued that modern systems are increasingly bottlenecked by data movement rather than compute, driven by exponential growth in datasets from domains like neural networks and genomics. He highlighted...

By Onur Mutlu Lectures

Video•Feb 18, 2026

Digital Design & Computer Architecture - Lecture 25: Prefetching (Spring 2022)

The penultimate lecture of the Spring 2022 Digital Design & Computer Architecture series focuses on prefetching – the proactive loading of data into cache or registers before it is demanded by the processor. The instructor emphasizes that prefetching is one of...

By Onur Mutlu Lectures

Video•Feb 17, 2026

Memory-Centric Computing - Talk at UCLA - 29.11.2022

Professor Onur Mutlu outlined the case for memory-centric computing, arguing that modern workloads—especially machine learning and genomics—generate far more data than current systems can efficiently process. He highlighted trends like wafer-scale processor designs and high-bandwidth memory attachments as steps toward...

By Onur Mutlu Lectures