Recent Posts

News•Mar 2, 2026

Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-Ppm Reliability

Researchers have demonstrated an 8 nm, 128 Mb embedded STT‑MRAM designed for automotive applications, achieving sub‑parts‑per‑million failure rates across the –40 °C to 150 °C temperature range. The cell area was aggressively scaled to 0.017 µm², while process refinements reduced short‑fail defects and enhanced MTJ stack thermal tolerance, widening read margins. Optimizations of the pinned‑layer and spin‑transfer torque efficiency delivered write error rates and retention errors below ppm levels without sacrificing speed, enabling 8 ns read operations. This milestone proves that high‑density memory can meet the stringent reliability standards required for advanced driver‑assistance and infotainment systems.

By SemiWiki

News•Mar 2, 2026

CEO Interview with Echo Yang of CSCERAMIC

CEO Echo Yang steers CSCERAMIC, a China‑based advanced ceramics maker, toward high‑purity alumina solutions for laboratory and high‑temperature industrial markets. The firm differentiates itself by engineering‑focused collaboration, tight dimensional control, and stable raw‑material sourcing rather than catalog sales. Customers benefit...

By SemiWiki

News•Feb 27, 2026

Memory Matters: Signals From the 2025 NVM Survey

The 2025 NVM Survey reveals that while embedded flash remains the default choice, awareness of alternatives such as MRAM, FRAM and ReRAM has risen above 25% among respondents. More than 80% of SoC designers are currently using or evaluating embedded...

By SemiWiki

News•Feb 26, 2026

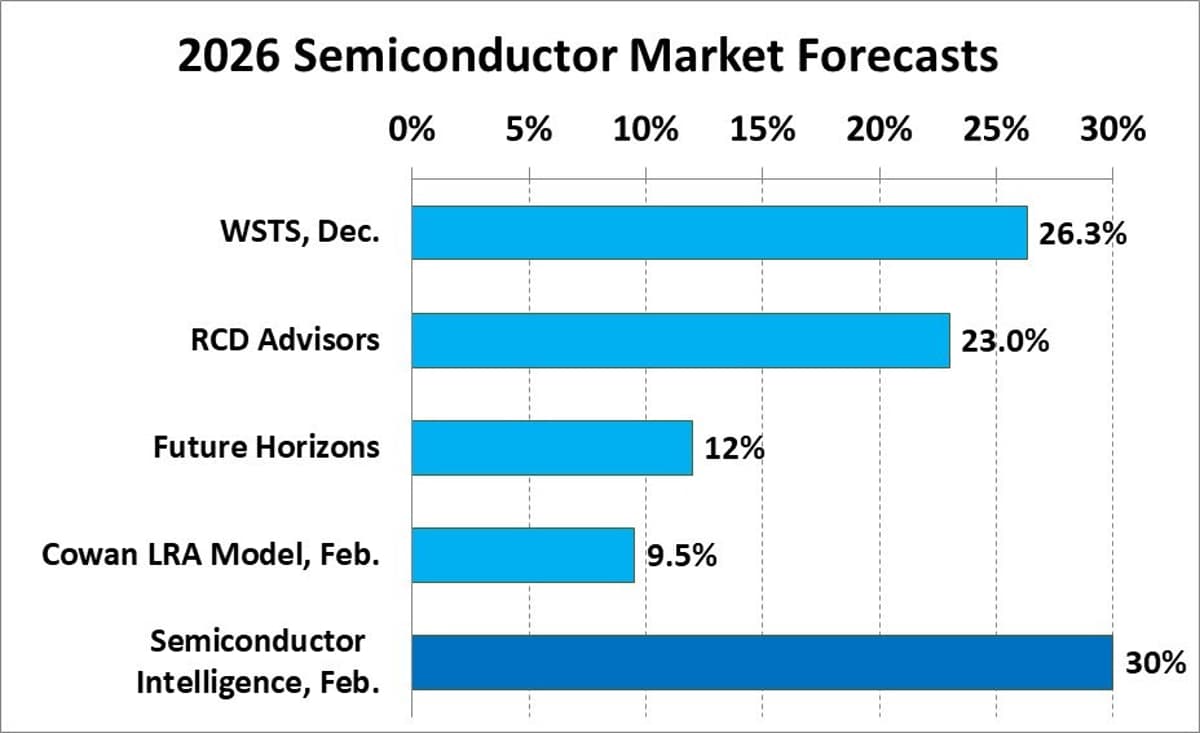

AI Drives Strong Semiconductor Market in 2025-2026

The global semiconductor market surged to $792 billion in 2025, a 25.6% year‑over‑year increase—the strongest since the COVID‑recovery spike in 2021. AI demand propelled Nvidia’s revenue up 65% and drove a collective 29% revenue rise among major memory makers. While most...

By SemiWiki

News•Feb 26, 2026

How Customized Foundation IP Is Redefining Power Efficiency and Semiconductor ROI

Synopsys is leveraging its Foundation IP platform to let semiconductor designers tailor standard cells, memory compilers, and EDA flows for specific workloads. In hyperscale AI servers, customized IP and optimized flows delivered up to 51% power reduction and a 5%...

By SemiWiki

News•Feb 26, 2026

Akeana Partners with Axiomise for Formal Verification of Its Super-Scalar RISC-V Cores

Akeana Inc. has teamed with formal‑verification specialist Axiomise to exhaustively verify its 4 nm super‑scalar RISC‑V test chip, Alpine. Using Axiomise’s CoreProve® framework, the collaboration identified functional bugs and redundant logic within months, enabling RTL optimizations before tape‑out. The formal approach...

By SemiWiki

News•Feb 26, 2026

An AI-Native Architecture That Eliminates GPU Inefficiencies

A recent MIT Technology Review analysis highlighted the massive energy footprint of generative‑AI inference, prompting a search for more efficient silicon. VSORA responded with a purpose‑built Matrix Processing Unit (MPU) that abandons the GPU‑centric SIMT model in favor of tensor‑level...

By SemiWiki

News•Feb 25, 2026

Caspia Technologies Unveils A Breakthrough in RTL Security Verification Paving the Way for Agentic Silicon Security

Caspia Technologies announced the general availability of CODAx V2026.1, an AI‑enhanced RTL security analyzer that checks over 150 insecure coding practices against more than 1,000 hardware vulnerability references. The tool can scan half‑million lines of RTL in under an hour,...

By SemiWiki

News•Feb 25, 2026

Designing the Future: AI-Driven Multi-Die Innovation in the Era of Agentic Engineering

At the 2026 Chiplet Summit, Synopsys unveiled an AI‑driven, agentic approach to multi‑die design that promises to automate and accelerate the entire workflow. The semiconductor industry is shifting toward heterogeneous chiplet architectures and 3‑D stacking, creating unprecedented design complexity. AI...

By SemiWiki

News•Feb 25, 2026

An Agentic Formal Verifier. Innovation in Verification

Infineon’s recent paper introduces Saarthi, an autonomous AI formal verification engineer that leverages multi‑agent LLM frameworks to generate, prove, and analyze RTL properties. The system creates English‑language verification plans, refines SystemVerilog assertions, and runs Cadence’s Jasper model‑checker in an iterative...

By SemiWiki

News•Feb 24, 2026

Reimagining Compute in the Age of Dispersed Intelligence

At the 2025 RISC‑V Summit, DeepComputing CEO Yuning Liang argued that AI will shift from cloud‑centric models to on‑device intelligence, leveraging aggressive quantization to run multiple models on a smartphone. He envisions a lightweight AI operating system that orchestrates models,...

By SemiWiki

News•Feb 24, 2026

Siemens to Deliver Industry-Leading PCB Test Engineering Solutions

Siemens announced the acquisition of ASTER Technologies, a specialist in PCB test and reliability solutions, to bolster its electronic design automation (EDA) portfolio. ASTER’s design‑for‑test, design‑for‑manufacturing, and design‑for‑reliability tools will be integrated into Siemens’ end‑to‑end digital‑thread platform, enabling earlier validation...

By SemiWiki

News•Feb 23, 2026

Hardware Is the Center of the Universe (Again)

The article traces four decades of hardware‑assisted verification (HAV) from its roots in 1980s in‑circuit emulation to today’s AI‑driven full‑stack validation platforms. Early emulators struggled with reliability but proved that pure software simulation could not keep pace with growing chip...

By SemiWiki

News•Feb 23, 2026

Smarter ECOs: Inside Easy-Logic’s ASIC Optimization Engine

Easy‑Logic Technology Ltd. has commercialized EasylogicECO, an automated functional Engineering Change Order (ECO) engine that generates minimal logic patches from RTL or specification updates. The tool leverages formal equivalence and optimization algorithms to preserve timing closure, layout integrity, and DFT...

By SemiWiki

News•Feb 23, 2026

TSMC Process Simplification for Advanced Nodes

Taiwan Semiconductor Manufacturing Co. (TSMC) disclosed Patent US10692720B2, which merges advanced EUV lithography with a controlled angled‑etch step to achieve sub‑35 nm end‑to‑end spacing. The method replaces the traditional three‑step lithography/etch flow with a single exposure, dramatically simplifying the process for...

By SemiWiki