From SoC to System-in-Package: Transforming Automotive Compute with Multi-Die Integration

Automotive electronics are moving from monolithic system‑on‑chips to multi‑die system‑in‑package solutions to meet soaring compute, safety, and longevity demands. By stacking or side‑by‑side heterogeneous dies, manufacturers can combine CPUs, GPUs, AI accelerators and high‑bandwidth memory within a single package. This approach improves scalability, yields and inter‑die bandwidth, addressing the limits of traditional SoCs for ADAS, autonomous driving and digital cockpits. Industry momentum is reinforced by zonal vehicle architectures and software‑defined platforms that require flexible, high‑performance compute blocks.

An Upper Bound on Effective Quantum Computation?

A recent PNAS paper argues that a fundamental limit exists on how many qubits can be meaningfully entangled, estimating an upper bound of roughly 1,000 logical qubits. The limit stems from a proposed discretization of space, which restricts the range...

YieldWerx Delivers a Master Class in Co-Packaged Photonics Implementation

YieldWerx announced a forthcoming webinar that will teach semiconductor engineers how to implement co‑packaged photonics (CPO) across the full product lifecycle. The session, led by CEO/CTO Aftkhar Aslam, will detail the 12 cross‑domain challenges—from optical data complexity to test‑flow discontinuities—and...

RISC-V Has Momentum. The Real Question Is Who Can Deliver

RISC‑V has moved from a promising ISA to a viable platform as the RVA23 baseline unifies high‑performance compute. Arm’s recent transition to a silicon‑first model reshapes the IP landscape, intensifying competition. Akeana’s Alpine test chip, taped out in a 4 nm...

CEO Interview with Jussi-Pekka Penttinen of Vexlum

Vexlum Ltd, a Finnish laser company co‑founded by Jussi‑Pekka Penttinen, unveiled its new VXL laser, a next‑generation VECSEL that delivers high‑power, single‑frequency output in a two‑liter package—up to ten times smaller than comparable systems. The wavelength‑agnostic platform can be customized...

CEO Interview with Dr. Tony Atti of Phononics

Phononic, led by CEO Dr. Tony Atti, is scaling solid‑state thermoelectric cooling across major hyperscalers to address the exploding thermal load of AI‑driven data centers. The company’s Thermal Kit combines fast‑acting TEC modules, software analytics and design services to deliver...

Silicon Catalyst and Microelectronics US 2026

Silicon Catalyst has been named the exclusive strategic partner for the Microelectronics US 2026 conference in Austin, Texas. The two‑day event, scheduled for April 22‑23, will bring together more than 3,000 engineers, investors, and policymakers to discuss semiconductor design, AI hardware, advanced...

Webinar – How to Reclaim Margin in Advanced Nodes

The ClockEdge webinar highlighted a hidden crisis in sub‑5 nm chip design: excessive guard‑banding caused by modeling uncertainty, which can strip 25‑35% of the clock period and cut performance‑per‑area (PPA) by up to 35%. Dave Johnson explained the “abstraction tax” and...

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor Technology

Alchip Technologies announced a dedicated 2nm ASIC design platform and completed a successful 2nm test‑chip tape‑out featuring its AP‑Link‑3D interface. The platform supports 2.5D and 3D chiplet integration, enabling high‑performance, power‑efficient silicon for AI and high‑performance computing workloads. By adopting...

CapEx Up for Foundry, Memory

Semiconductor Intelligence projects total industry capital spending to reach $200 billion in 2026, a 20% rise from 2025 and outpacing market growth. TSMC remains the largest spender, targeting $52‑$56 billion, while most other foundries stay flat except GlobalFoundries’ 70% increase. Elon Musk’s...

RISC-V Now! — Where Specification Meets Scale!

RISC‑V Now! is a Silicon Valley conference designed to turn the open RISC‑V instruction set architecture into shipped products at scale. The event attracted roughly 600 semiconductor professionals from more than 250 companies, including industry giants such as Apple, Google,...

Nuclear Power and Design Automation

Nuclear energy is gaining renewed attention as data‑center power demand surges, with small modular reactors (SMRs) offering a cost‑effective alternative to traditional plants. SMRs are projected to cost $2.5‑4 B, far less than the $30 B required for full‑size reactors, while molten‑salt...

CEO Interview with Charlie Peppiatt of Gooch & Housego

Gooch & Housego (G&H) is a global photonics engineering firm that designs and manufactures high‑performance optical components, subsystems, and systems across the full value chain. Charlie Peppiatt, who joined as CEO in September 2022 after leading TT Electronics and Stadium Group,...

Sensors Converge: Where Intelligence Meets the Edge

The Sensors Converge Conference showcased the latest advances in sensor miniaturization, edge AI, power management, and secure connectivity across multiple industries. Attendees highlighted how system‑in‑package designs and heterogeneous integration are delivering compact, low‑cost modules that combine temperature, pressure, inertial and...

Silicon Insurance: Why eFPGA Is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era

As semiconductor nodes become ever more complex, the financial risk of ASIC respins has surged, with mask sets at Intel’s 18A process costing tens of millions of dollars. Embedded FPGA (eFPGA) offers "silicon insurance" by embedding reconfigurable logic that can...

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry

Researchers at imec presented new findings on metal‑oxide resists (MORs) for EUV lithography, showing that atmospheric oxygen, not CO₂ or humidity, drives post‑exposure chemical changes. Using the BEFORCE platform, they demonstrated that O₂ induces carbonyl formation and accelerates ligand loss...

Post-Silicon Validating an MMU. Innovation in Verification

A recent IBM paper extends post‑silicon validation to the memory management unit (MMU) using Cadence’s Threadmill bare‑metal exerciser. The method generates multi‑threaded, constraint‑driven tests that run indefinitely on first silicon, stressing TLB walks, page‑table updates, context switches and migrations. In...

Securing UALink in AI Clusters with UALinkSec-Compliant IP

Synopsys announced the UALinkSec_200 Security Module, the first hardware implementation that complies with the UALink 200 G specification’s security framework. The module provides end‑to‑end AES‑GCM encryption and authentication at the full 200 GT/s lane rate, integrating with Synopsys’ UALink controller IP and...

GTC 2026: Agentic AI for Semiconductor Design and Manufacturing

Agentic AI is emerging as an autonomous layer for semiconductor design and manufacturing, building on decades of heuristic, machine‑learning, and generative‑AI advances. By orchestrating specialized agents across specification, microarchitecture, verification, and physical implementation, firms report up to ten‑fold acceleration of...

Scaling Multi-Die Connectivity: Automated Routing for High-Speed Interfaces

The article wraps up a three‑part series on multi‑die design by highlighting automated routing as the next critical step for high‑speed die‑to‑die interfaces such as High‑Bandwidth Memory (HBM) and Universal Chiplet Interconnect Express (UCIe). It explains how dense bump maps...

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet Summit

At the Chiplet Summit, Arteris highlighted its multi‑die interconnect portfolio, showcasing FlexGen, FlexNoC and the coherent Ncore platform for AI, HPC and automotive ADAS applications. The solutions support up to four die‑to‑die links per chiplet and flexible sub‑assembly configurations, enabling...

CEO Interview with Moti Margalit of SonicEdge

SonicEdge, led by CEO Moti Margalit, is commercializing a solid‑state speaker that uses modulated 400 kHz ultrasound to generate full‑range audio from a 6.5 × 4 × 1 mm MEMS die. The company holds more than 28 patents and announced a development contract with a leading...

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?

Elon Musk turned a dead GM‑Toyota plant into the highest‑volume auto factory in North America, proving that cultural overhaul can revive failing manufacturing assets. The U.S. semiconductor sector now faces a similar crisis: Intel, Samsung and other fabs suffer from...

WEBINAR: HBM4E Advances Bandwidth Performance for AI Training

Rambus unveiled its HBM4E memory‑controller IP, targeting the bandwidth bottleneck that AI‑training GPUs face. The new controller delivers the full 16 Gb/s per pin, equating to roughly 4.1 TB/s per device, a two‑fold speed increase over HBM4. In a webinar, Director Nadish Kamath...

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design Enablement

Siemens EDA’s Innovator3D IC solution captured the Best in Show award for packaging design at the Chiplet Summit in Santa Clara. The platform offers a unified, system‑level flow that spans design planning, implementation, verification, and manufacturing for heterogeneous 3D ICs. Siemens highlighted...

Accelerating Computational Lithography Using Massively Parallel GPU Rasterizer

Siemens EDA unveiled a GPU‑accelerated rasterization algorithm that transforms computational lithography workflows. By decomposing layouts into tiles and processing them on NVIDIA H100 GPUs, the method attains speedups of up to 290× for Manhattan geometries and 45× for curvilinear designs....

Breker Hosts an Energetic Panel on Spec-Driven Verification

At DVCon 2026, Breker hosted a panel on AI‑driven, spec‑driven SoC verification featuring leaders from Moores Lab, Breker, Arm, and Intel. Participants highlighted that AI can translate raw specifications into intermediate representations with roughly 90‑95% accuracy, but emphasized the need for...

Formal Verification Best Practices

Formal verification offers an exhaustive, mathematical approach to prove hardware designs meet specifications, complementing traditional simulation. Siemens’ white paper outlines best practices such as writing simple assertions, using assumptions to limit state space, and applying abstraction techniques like memory black‑boxing....

WEBINAR: Reclaiming Clock Margin at 3nm and Below

At 3 nm and smaller, clock networks have become the primary limiter of SoC power, performance, and yield, yet most designs still use legacy abstraction‑based sign‑off methods. These methods introduce 25‑35% guard‑band overhead, with 10‑15% of the clock period being unnecessary...

AI-Driven Automation in Semiconductor Design: The Fuse EDA AI Agent

Siemens has launched the Fuse EDA AI Agent, an agentic AI platform that automates and optimizes electronic design automation across the full chip development lifecycle. The system targets the soaring complexity of modern SoCs, where design costs can exceed $300 million...

TSMC Technology Symposium 2026: Advancing the Future of Semiconductor Innovation

TSMC’s 32nd Technology Symposium in Santa Clara showcased its roadmap toward 2 nm‑class and angstrom‑era processes, highlighted by the upcoming A16 node slated for production in the second half of 2026. The event emphasized AI and high‑performance computing workloads, demonstrating how...

Synopsys Explores AI/ML Impact on Mask Synthesis at SPIE 2026

Synopsys hosted a Lithography VIP Symposium at SPIE 2026, featuring a panel on AI/ML in mask synthesis. Executives from photomask makers, fabs, and EDA discussed how GPUs and advanced AI are already addressing the exploding complexity of EUV mask design....

Unraveling Dose Reduction in Metal Oxide Resists via Post-Exposure Bake Environment

Researchers at imec introduced the BEFORCE platform to study how post‑exposure bake (PEB) environments affect metal‑oxide EUV resists. By precisely mixing oxygen, humidity, and other gases, they demonstrated that raising O₂ to 50 % and adjusting relative humidity can lower the...

CEO Interview with Dr. Mohammad Rastegari of Elastix.AI

Elastix.AI, led by former Meta and Apple AI scientist Dr. Mohammad Rastegari, is building a reconfigurable FPGA‑based inference platform that promises dramatically lower cost and power consumption for large‑scale AI models. The company claims up to ten‑fold reductions in inference...

Agentic AI and the Future of Engineering

At Synopsys' Converge keynote, Sassine Ghazi introduced "agentic AI" as a practical layer that augments engineers rather than replaces them, addressing the mounting complexity of chip and system design. He outlined a five‑level autonomy roadmap (L1‑L5) that moves from simple...

Ravi Subramanian on Trends that Are Shaping AI at Synopsys

Ravi Subramanian, Synopsys' Chief Product Management Officer, explained how AI is driving the convergence of silicon design and systems engineering, a shift highlighted at the Synopsys Converge event. He noted the industry’s move from throughput‑focused metrics to efficiency‑centric measures such...

Axiomise Introduces nocProve to Transform NoC Design Verification

Axiomise has launched nocProve, the first configurable formal verification application dedicated to Network-on-Chip (NoC) designs. The tool leverages the company’s proprietary proof engine to exhaustively prove correctness across multiple clock domains, virtual channels, and routing schemes. By automating proof generation...

Qnity and Silicon Catalyst Light a Path to Success at the Chiplet Summit

The Chiplet Summit highlighted the accelerating shift toward multi‑die heterogeneous designs, with chiplets emerging as a pivotal enabler. Silicon Catalyst showcased its unique global accelerator that moves semiconductor startups from concept to product, featuring a standout session on its partner...

Operationalizing Secure Semiconductor Collaboration: Safely, Globally, and at Scale

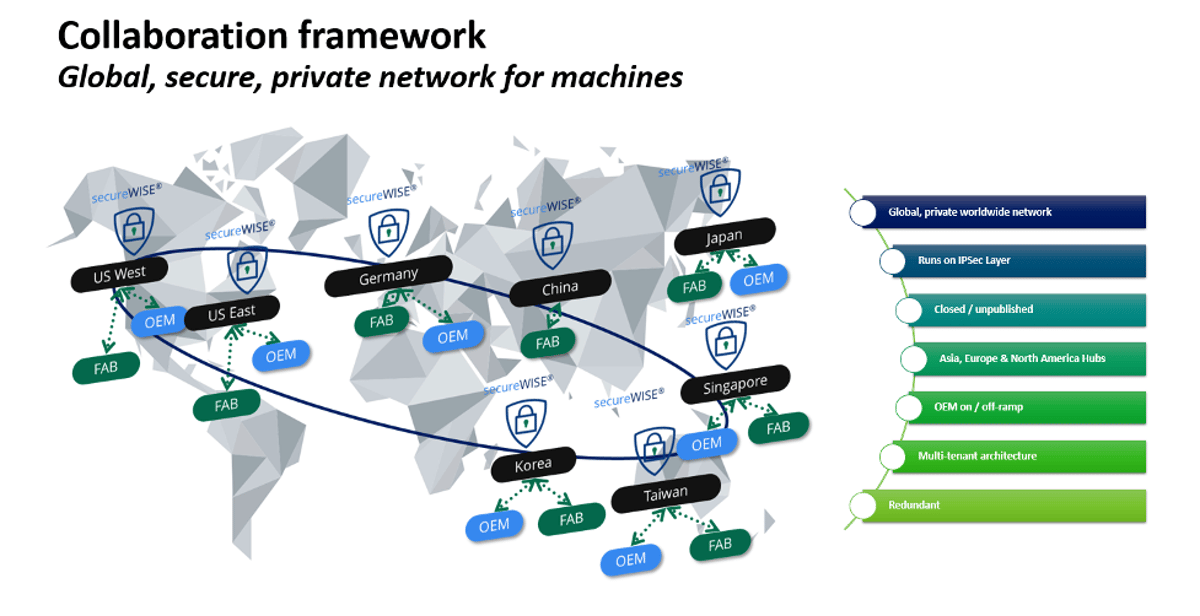

Semiconductor fabs now face a massive cyber‑attack surface as software components proliferate across thousands of suppliers. Traditional isolation and ad‑hoc VPNs can’t keep pace with rapid patching needs, leaving long exposure windows. Industry standards such as SEMI E187/E188/E191 set a...

Keynote: On-Package Chiplet Innovations with UCIe

The Universal Chiplet Interconnect Express (UCIe) was unveiled at Chiplet Summit 2026 as an open standard that standardizes on‑package chiplet connections, positioning System‑in‑Package as the new SoC. Since its 2022 launch, the consortium has grown to over 140 members and...

CEO Interview with Jerome Paye of TAU Systems

TAU Systems, led by CEO Jerome Paye, is developing compact laser‑driven particle accelerators that generate X‑ray free‑electron lasers for semiconductor lithography. The technology promises shorter wavelengths, higher power and dramatically lower cost than today’s $400 million EUV machines. In the short...

Things From Intel 10K That Make You Go …. Hmmmm

Intel’s 2025 Form 10‑K reveals manufacturing constraints centered on its Intel 7 process rather than external partners like TSMC. Gross margins sit near 35 percent, yet GAAP operating margins turned negative after a large legacy asset write‑down and depreciation changes. The Foundry division...

RVA23 Ends Speculation’s Monopoly in RISC-V CPUs

RVA23 declares the RISC‑V Vector Extension (RVV) a mandatory feature, turning explicit vector parallelism into a baseline capability for all compliant CPUs. By offloading throughput work to deterministic vector units, scalar cores can become simpler, low‑power coordinators without sacrificing performance....

Building the Interconnect Foundation: Bump and TSV Planning for Multi-Die Systems

Bump and TSV planning underpins the electrical and mechanical fabric of multi‑die systems, enabling the ultra‑high bandwidth and low latency required for chiplet architectures. As interconnect pitch shrinks, designs can involve millions of contacts, making manual spreadsheet methods infeasible and...

CHERI: Hardware-Enforced Capability Architecture for Systematic Memory Safety

CHERI (Capability Hardware Enhanced RISC Instructions) introduces a hardware‑enforced capability architecture that replaces raw pointers with bounded, unforgeable references, making out‑of‑bounds memory accesses architecturally impossible. The design adds only about 4‑5% processor area and incurs minimal performance loss, while allowing...

WEBINAR: Two-Part Series on RF Power Amplifier Design

The RF power‑amplifier landscape has shifted from simple scalar load‑pull to sophisticated vector and simulated techniques as mmWave and sub‑THz designs demand tighter margins and wider bandwidths. Keysight’s two‑part masterclass introduces a VNA‑inspired load‑pull method that uses a‑ and b‑waves...

Securing RISC-V Third-Party IP: Enabling Comprehensive CWE-Based Assurance Across the Design Supply Chain

RISC‑V adoption drives the need for third‑party IP security. Arteris (formerly Cycuity) introduced a CWE‑based assurance framework that translates MITRE weaknesses into reusable security requirements, verification properties, and portable C‑tests. A pilot with SiFive’s X280 core analyzed 16 of 60...

Apple’s iPhone 17 Series 5G mmWave Antenna Module Revealed to Be Powered by Soitec FD-SOI Substrates

Independent teardowns confirm that Apple’s iPhone 17, 17 Pro and 17 Pro Max use Qualcomm’s QTM565 mmWave antenna‑in‑package module, which is fabricated on Soitec’s Fully Depleted Silicon‑On‑Insulator (FD‑SOI) substrate via GlobalFoundries’ 22FDX process. The finding validates FD‑SOI as a high‑volume substrate for FR2 5G...

Advancing Automotive Memory: Development of an 8nm 128Mb Embedded STT-MRAM with Sub-Ppm Reliability

Researchers have demonstrated an 8 nm, 128 Mb embedded STT‑MRAM designed for automotive applications, achieving sub‑parts‑per‑million failure rates across the –40 °C to 150 °C temperature range. The cell area was aggressively scaled to 0.017 µm², while process refinements reduced short‑fail defects and enhanced MTJ...

CEO Interview with Echo Yang of CSCERAMIC

CEO Echo Yang steers CSCERAMIC, a China‑based advanced ceramics maker, toward high‑purity alumina solutions for laboratory and high‑temperature industrial markets. The firm differentiates itself by engineering‑focused collaboration, tight dimensional control, and stable raw‑material sourcing rather than catalog sales. Customers benefit...