An AI-Native Architecture That Eliminates GPU Inefficiencies

A recent MIT Technology Review analysis highlighted the massive energy footprint of generative‑AI inference, prompting a search for more efficient silicon. VSORA responded with a purpose‑built Matrix Processing Unit (MPU) that abandons the GPU‑centric SIMT model in favor of tensor‑level execution. By using a massive on‑chip register file and deterministic pipelining, the MPU eliminates thread‑management overhead and cache‑miss penalties, delivering high utilization even at batch size 1. The architecture integrates seamlessly with TensorFlow, PyTorch and ONNX, offering immediate performance gains without code rewrites.

Caspia Technologies Unveils A Breakthrough in RTL Security Verification Paving the Way for Agentic Silicon Security

Caspia Technologies announced the general availability of CODAx V2026.1, an AI‑enhanced RTL security analyzer that checks over 150 insecure coding practices against more than 1,000 hardware vulnerability references. The tool can scan half‑million lines of RTL in under an hour,...

Designing the Future: AI-Driven Multi-Die Innovation in the Era of Agentic Engineering

At the 2026 Chiplet Summit, Synopsys unveiled an AI‑driven, agentic approach to multi‑die design that promises to automate and accelerate the entire workflow. The semiconductor industry is shifting toward heterogeneous chiplet architectures and 3‑D stacking, creating unprecedented design complexity. AI...

An Agentic Formal Verifier. Innovation in Verification

Infineon’s recent paper introduces Saarthi, an autonomous AI formal verification engineer that leverages multi‑agent LLM frameworks to generate, prove, and analyze RTL properties. The system creates English‑language verification plans, refines SystemVerilog assertions, and runs Cadence’s Jasper model‑checker in an iterative...

Reimagining Compute in the Age of Dispersed Intelligence

At the 2025 RISC‑V Summit, DeepComputing CEO Yuning Liang argued that AI will shift from cloud‑centric models to on‑device intelligence, leveraging aggressive quantization to run multiple models on a smartphone. He envisions a lightweight AI operating system that orchestrates models,...

Siemens to Deliver Industry-Leading PCB Test Engineering Solutions

Siemens announced the acquisition of ASTER Technologies, a specialist in PCB test and reliability solutions, to bolster its electronic design automation (EDA) portfolio. ASTER’s design‑for‑test, design‑for‑manufacturing, and design‑for‑reliability tools will be integrated into Siemens’ end‑to‑end digital‑thread platform, enabling earlier validation...

Hardware Is the Center of the Universe (Again)

The article traces four decades of hardware‑assisted verification (HAV) from its roots in 1980s in‑circuit emulation to today’s AI‑driven full‑stack validation platforms. Early emulators struggled with reliability but proved that pure software simulation could not keep pace with growing chip...

Smarter ECOs: Inside Easy-Logic’s ASIC Optimization Engine

Easy‑Logic Technology Ltd. has commercialized EasylogicECO, an automated functional Engineering Change Order (ECO) engine that generates minimal logic patches from RTL or specification updates. The tool leverages formal equivalence and optimization algorithms to preserve timing closure, layout integrity, and DFT...

TSMC Process Simplification for Advanced Nodes

Taiwan Semiconductor Manufacturing Co. (TSMC) disclosed Patent US10692720B2, which merges advanced EUV lithography with a controlled angled‑etch step to achieve sub‑35 nm end‑to‑end spacing. The method replaces the traditional three‑step lithography/etch flow with a single exposure, dramatically simplifying the process for...

CEO Interview with Juniyali Nauriyal of Photonect

Photonect, a Rochester‑based photonics startup founded by CEO Juniyali Nauriyal, is commercializing a laser‑fusion, epoxy‑free fiber‑to‑chip attachment process. The technology, built around an oxide mode converter, lifts coupling efficiency from roughly 50 % to 80 % and cuts optical loss to under...

What Is the 3nm Pessimism Wall and Why Is It An Economic Crisis?

The article defines the “3 nm Pessimism Wall” as the excessive 25‑35% clock‑period guard bands that arise from abstraction‑based sign‑off methods rather than physical limits. These inflated margins force over‑design of buffers, increase power consumption, and waste silicon area, turning advanced‑node...

CEO Interview with Aftkhar Aslam of yieldWerx

YieldWerx, led by semiconductor veteran Aftkhar Aslam, offers a data‑centric yield‑analytics platform that consolidates fragmented fab, test, and packaging information into a single, actionable environment. The solution tackles extreme data volumes and multi‑domain complexity, supporting advanced packaging, silicon photonics, MicroLED,...

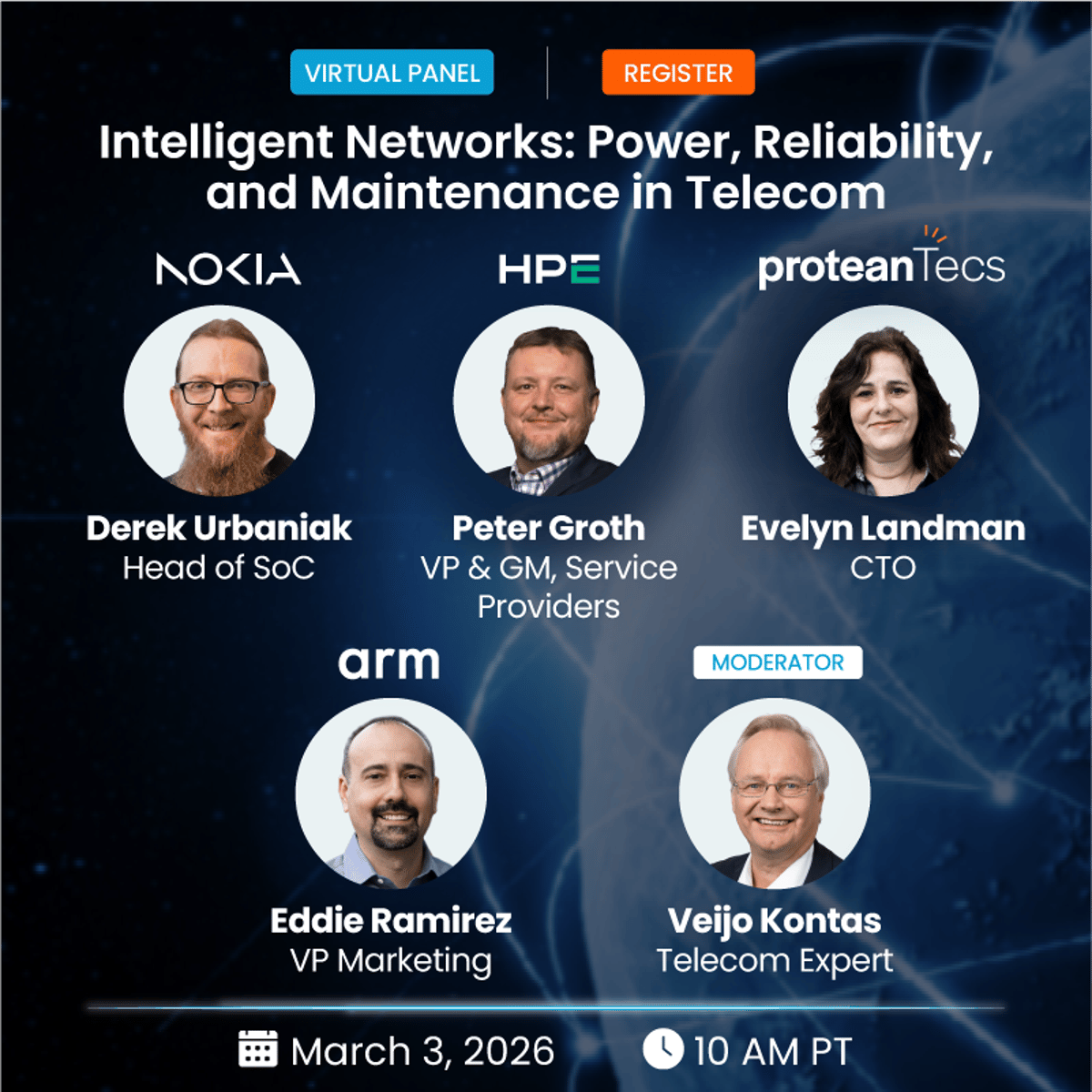

Intelligent Networks: Power, Reliability, and Maintenance in Telecom — Webinar Preview

The upcoming webinar "Intelligent Networks: Power, Reliability, and Maintenance in Telecom" will explore how telecom operators can leverage AI, real‑time analytics, and automation to tackle rising energy costs, ensure ultra‑reliable service, and modernize maintenance. It highlights the shift toward cloud‑native,...

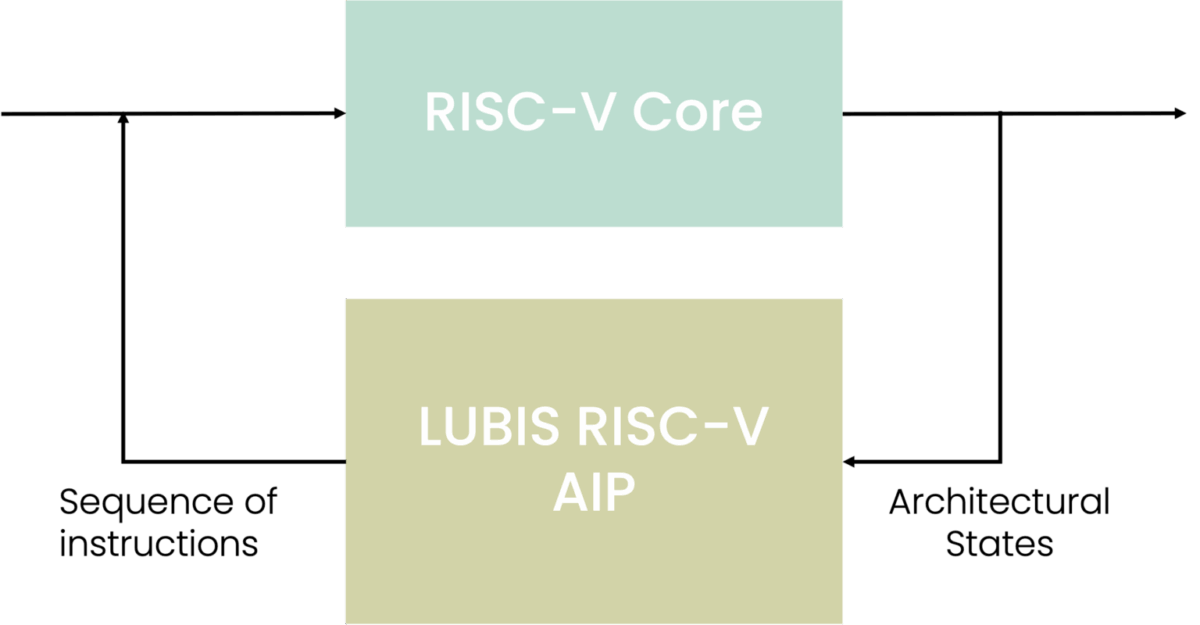

LUBIS EDA: Addressing the Verification Bottleneck in Modern Chip Design

Verification has become the primary bottleneck in modern chip design, as simulation struggles to cover the exponential state space of AI, HPC, and automotive processors. Formal verification offers exhaustive proof of design properties but traditionally required manual assertions and specialist...

Ceva IP: Powering the Era of Physical AI

Ceva IP is positioning itself as the core enabler of Physical AI, delivering integrated semiconductor and software IP that brings sensing, connectivity, and on‑device inference to edge devices. By moving AI processing from the cloud to the chip, its solutions...

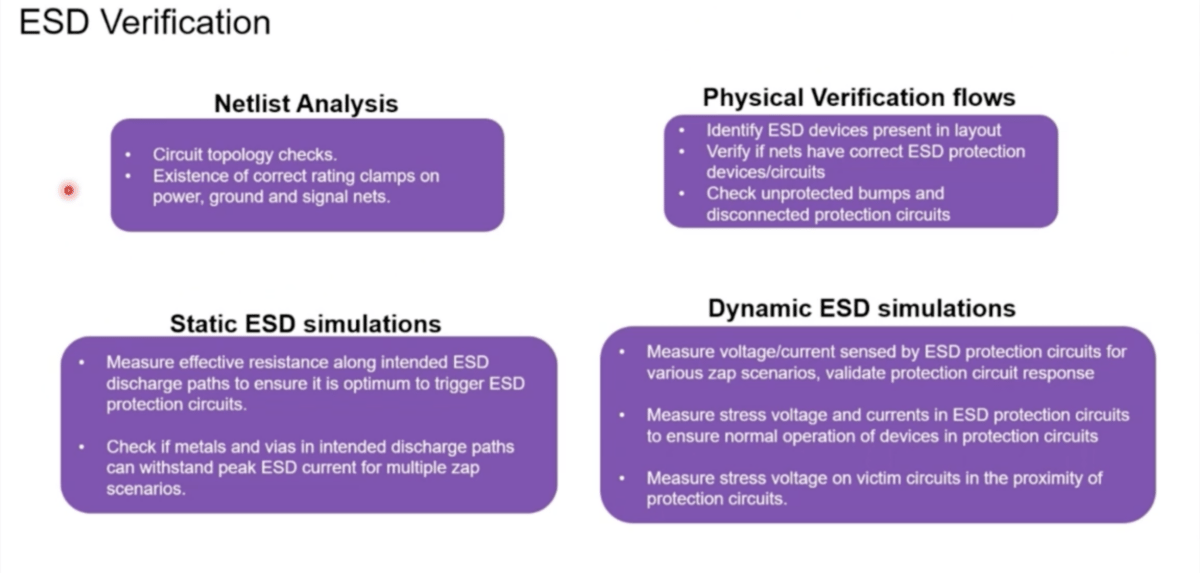

Accelerating Static ESD Simulation for Full-Chip and Multi-Die Designs with Synopsys PathFinder-SC

Synopsys unveiled PathFinder‑SC, a static ESD verification platform that enables early, layout‑driven analysis for full‑chip and multi‑die designs. Leveraging cell‑based modeling from GDS/DEF data and the Seascape distributed‑computing engine, the tool can simulate billions of nodes and complete complex resistance...

A Century of Miracles: From the FET’s Inception to the Horizons Ahead

2025 marks the centennial of the field‑effect transistor, first patented by Julius Lilienfeld in 1925. After decades of material and physics challenges, MOSFET stability was achieved in 1969, launching the era of large‑scale integration and the scaling roadmap defined by...

Two Open RISC-V Projects Chart Divergent Paths to High Performance

Two open‑source RISC‑V projects—ETH Zürich’s Ara vector processor and China’s XiangShan scalar core—demonstrate opposite strategies for scaling performance. Ara implements the RISC‑V Vector Extension with explicit parallelism and no speculation, relying on software‑managed locality and a shallow memory hierarchy. XiangShan...