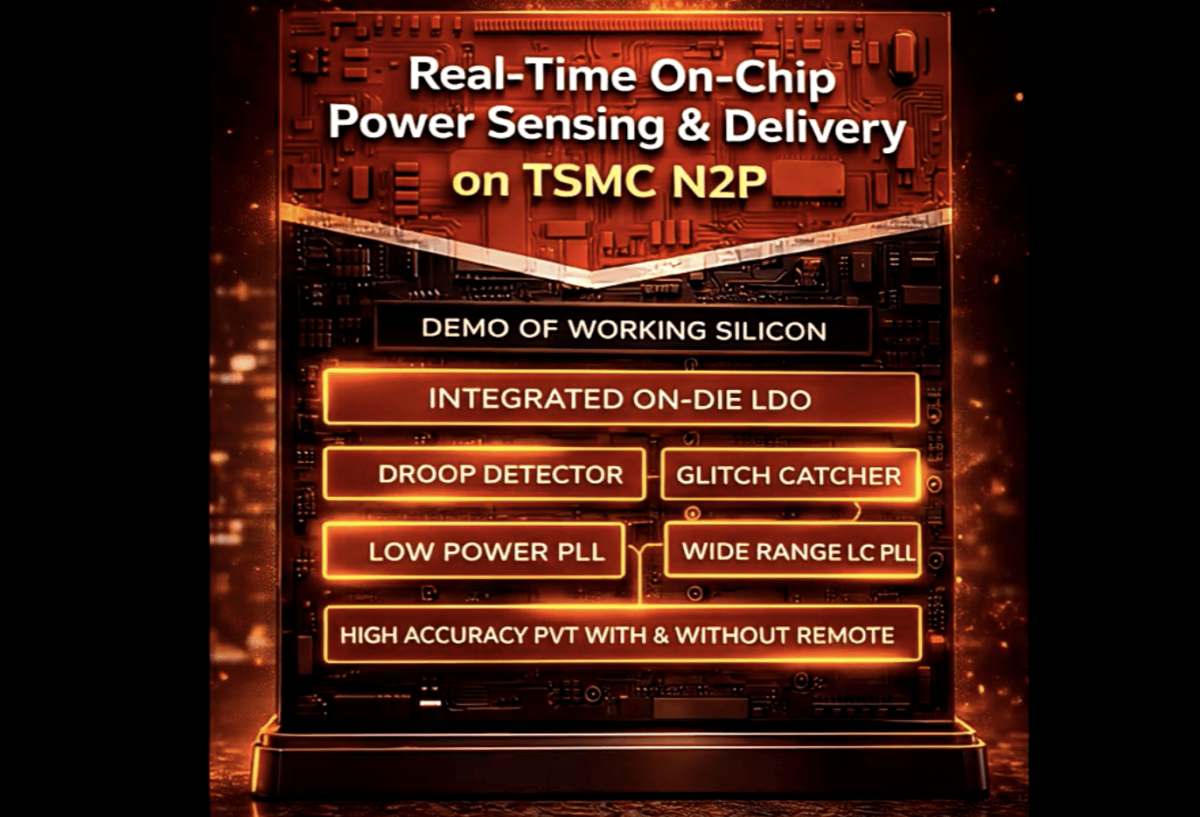

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology Symposium

Key Takeaways

- •Analog Bits showcases 12+ IP blocks on TSMC N2P process

- •On‑die LDO cuts area 30% with ultra‑high bandwidth

- •New pinless PVT sensors achieve ±3.5 °C accuracy untrimmed

- •Microwatt PLLs operate at 0.5 µW/MHz for ultra‑low power

- •Real‑time power sensing enables instant corrective actions for AI/HPC chips

Pulse Analysis

Power density is becoming the bottleneck for AI accelerators and high‑performance computing (HPC) silicon as manufacturers push transistor scaling into the sub‑5 nm regime. Traditional voltage regulation and thermal management schemes, which rely on off‑chip components, can no longer keep pace with the rapid voltage swings and localized heating of multi‑kilowatt system‑on‑chips (SoCs). Engineers are therefore turning to on‑die power management solutions that can sense, react, and optimize power delivery in real time, reducing latency and improving overall efficiency.

Analog Bits’ showcase at the TSMC 2026 Technology Symposium illustrates how advanced analog IP can address these challenges. The company’s on‑die linear regulator (LDO) delivers a 30% area reduction while maintaining ultra‑high bandwidth, enabling tighter voltage control for high‑performance CPU cores and SERDES lanes. Complementary blocks such as the droop detector, glitch catcher, and ultra‑low‑power PLLs provide continuous monitoring and rapid corrective action, while pinless PVT sensors achieve ±3.5 °C accuracy without trimming, delivering precise temperature and process data directly on the chip. Together, these 12+ IPs create a holistic power‑aware architecture that can be integrated into TSMC’s N2P process, a node optimized for AI and HPC workloads.

The broader market impact is significant. By embedding power regulation and sensing directly into silicon, designers can lower board‑level component counts, reduce form factor, and improve reliability—key differentiators for data‑center servers and edge AI devices. As TSMC’s N2P node gains traction, Analog Bits’ IP portfolio positions the company as a strategic partner for fabless firms seeking to maximize performance‑per‑watt metrics. The real‑time capabilities demonstrated at the symposium are likely to accelerate adoption across the AI chip ecosystem, driving a new wave of power‑efficient, high‑density compute platforms.

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology Symposium

Comments

Want to join the conversation?